Распараллеливание вычислительных процессов – одно из возможных решений проблемы повышения производительности. Однако производительность стандартных методов построения параллельных вычислений, обычно не превышает 10–15% от указанной пиковой производительности. Это обусловлено тем, что жесткая архитектура ВС часто не соответствует информационной структуре решаемой задачи. Для преодоления сложившейся ситуации и используется способ построения гибкой реконфигурируемой системы на базе FPGA (Field-Programmable Gate Array) с управляющими процессорами [1, 3, 4].

Разработка и увеличение логики в FPGA позволяет применять более сложные алгоритмы, которые можно запрограммировать в микросхему. Подключение такого типа FPGA к современному процессору через высокоскоростную шину, например, PCI Express, позволило конфигурируемой логике действовать больше как сопроцессор, а не периферийное устройство. Это привело к реконфигурируемости в сфере высокопроизводительных вычислений.

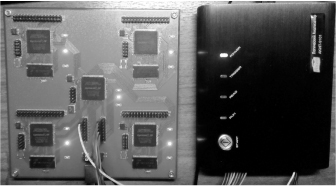

В данной статье РВС это устройство, состоящее из 4 реконфигурируемых процессоров, реализованных на FPGA [2, 6]. Разработка подобной системы на FPGA предоставляет возможность для реконфигурации устройства под различные классы задач цифровой обработки сигнала, и обработки больших массивов данных.

Разрабатывая многопроцессорную вычислительную систему (МПВС), инженеры сталкиваются с проблемой, уменьшения потерь при планировании процессов. Назначение процессов или потоков по процессорным узлам в планировщике выполняет функция диспетчеризации задач [7, 9, 10].

В МПВС с глобальной очередью диспетчер выполняется программно посредством вызова этих функций из общей памяти, где расположена программа ОС.

Являясь достаточно быстрой, программная реализация в пространстве пользователя имеет сложную структуру, так как для произведения сопряженной с диспетчеризацией процедуры синхронизации необходимо 3 семафора. Первый счетчик, который считает число мест, занятых готовых к обработке процессами, второй счетчик, считает количество процессоров, находящихся на обслуживании, третий это мьютекс для функции взаимного исключения, останавливающего одновременный доступ некоторых свободных процессоров к одной очереди, которая является в виде общего ресурса.

Чтобы разрешить этот вопрос используют метод синхронизации в пространстве ядра, но повышенные временные затраты сильно уменьшают производительность МПВС.

Оптимальное решение вышеописанных проблем заключается в аппаратной реализации функции синхронизации, так как это снимает ответственность за выполнение данных функции с процессорных узлов, что повышает производительность, достигается увеличение надежности ОС [8].

Предложенный метод основан на том, что функция диспетчера задач будет выполнена в виде независимого специализированного процессора в составе реконфигурируемой вычислительной системы.

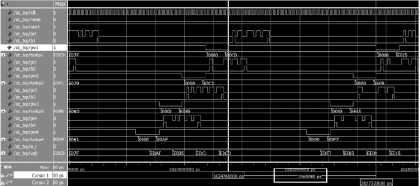

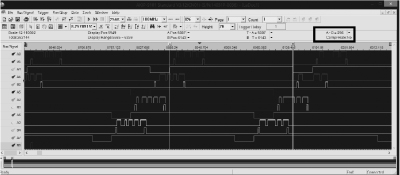

Для экспериментального моделирования, спроектированного ДЗ, были созданы блоки имитации 4 процессоров и блок генератора задач. Моделирование проводилось с помощью ПО ModelSim-Altera 10.0c. [5, 11] После компиляции была запущена симуляция проекта. Также проводилось моделирование с помощью лабораторного стенда, который включает в себя логический анализатор АКИП-9101, опытный образец разрабатываемой РВС (рис. 2). По результатам проведения экспериментов были получены временные диаграммы (рис. 1, 3) работы системы с диспетчером задач.

Представленные временные диаграммы на рис. 1 показывают, что идентификатор поступившей задачи под номером EDAF передался на обработку в процессор под номером 4 (taskp4), Процессор под номером 4 оказался занятым, поэтому следующий идентификатор задачи EDB5 принят на обработку в третий процессор.

По результатам моделирования видно, что первым для обслуживания текущей задачи назначен четвертый процессор, следом назначается третий процессор, и так далее. Это обусловлено схемой приоритетов от выполнения задач в системе, т.е. от четвертого процессора к первому. Для верификации разработанного алгоритма и полученных временных диаграмм в среде моделирования ModelSim-Altera 10.0c, проведен эксперимент на основе аппаратной платформы опытного образца РВС.

Рис. 1. Диаграммы работы системы в среде моделирования ModelSim-Altera 10.0c

Рис. 2. Стенд для проведения эксперимента

Рис. 3. Временные диаграммы, полученные с помощью логического анализатора

По результатам эксперимента можно заключить, что алгоритм работы диспетчера действительно работает, что видно из временных показаний выполнения работы процессора (сигнал pw1, сигнал A4 на рис. 1 и 3 соответственно) который составляет 256 тактовых отсчетов или 2560 нс.