В статье описана структура цифрового адаптера магистрального параллельного интерфейса (МПИ). (рисунок). Разработанный блок представляет собой вычислительную систему, монтируемую на печатную плату, и предназначен для обеспечения информационного обмена между ЭВМ типа с внешними устройствами по МПИ – стандарту, определяющему набор контактов и процедуры обмена по 16-разрядной шине с мультиплексированием адреса и данных. в соответствии с ГОСТ 26765.51–86. Указанный блок представляет собой полностью законченный модуль, являющийся устройством на шине PCI и функционирующим в соответствии со спецификацией шины PCI с поддержкой протокола Plug&Play на частоте до 33 (66) МГц. Управление работой и информационный обмен осуществляется через порты ввода-вывода и ОЗУ двойного доступа (ОЗУ ДД).

Рассмотрим вычислительную систему, состоящую из цифрового адаптера МПИ, контроллера прерываний, памяти и периферийных устройств (оборудования). Цифровой адаптер МПИ выполняет роль процессора в рассматриваемой системе. Все арифметические и логические операции проходят обработку именно в нем. Созданный цифровой модуль может осуществлять операции передачи управления шиной, адресного обмена, прерывания (одноуровневая система прерываний, четырехуровневая система прерываний). Работа цифрового адаптера МПИ происходит по ГОСТ 26765. 51–86 [1, 2, 3].

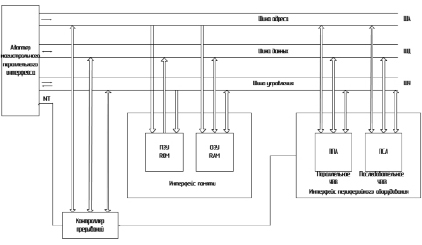

Вычислительная система с адаптером магистрального параллельного интерфейса

Описываемая в статье вычислительная система состоит из следующих основных блоков: цифровой адаптер МПИ, контроллер прерываний, память, периферийные устройства. Для большинства современных микропроцессоров характерно наличие трехшинной структуры, содержащей шину адреса (ША), двунаправленную шину данных (ШД) и шину управления (ШУ) [4, 5]. Как видно из представленной структурной схемы типовая система предполагает наличие общего сопряжения для модулей памяти (постоянных и оперативных запоминающих устройств) [6, 7, 8] и устройств ввода-вывода.

В качестве периферийных устройств в аналогичных системах используются устройства ввода с клавиатуры и различных датчиков, вывода на дисплеи, ввода-вывода на сетевые карты, модемы и т.п.

Периферийное устройство соединяется с шинами МП не непосредственно, а через программируемый периферийный адаптер (ППА) или программируемый связной адаптер (ПСА), обслуживающие периферию соответственно с передачей информации параллельным или последовательным кодом. Наличие программно настраиваемых адаптеров делает весьма гибкой и функционально богатой систему ввода-вывода информации в МП-системе.

Постоянное запоминающее устройство (ПЗУ) хранит системные программы, необходимые для управления процессом обработки. В оперативном запоминающем устройстве (ОЗУ) хранятся прикладные программы, данные и результаты вычислений.

Работа рассматриваемого цифрового адаптера МПИ синхронизируется тактовыми частотами в 33 или 66) МГц (CLK33 (или CLK66)), поступающими на его входы от разъема PCI.

В предлагаемой структуре цифрового адаптера МПИ реализуются три способа организации передачи информации:

1) программно-управляемая передача, инициируемая самим цифровым адаптером (процессором);

2) программно-управляющая передача, инициируемая запросом прерывания от периферийного устройства к цифровому адаптеру;

3) прямой доступ к памяти (ПДП).

При первом упомянутом способе передача инициируется самим цифровым адаптером, а при втором – запросом прерывания от периферийного устройства.

Прямым доступом к памяти называется способ обмена данными, обеспечивающий автономно от цифрового устройства установление связи и передачу данных между ОЗУ и внешним устройством.

Прямой доступ к памяти, повышая предельную скорость ввода-вывода информации и общую производительность системы, делает ее более приспособленной для работы в системах реального времени (СРВ). Прямым доступом к памяти управляет контролер ПДП, на который возложено выполнение следующих функций:

– управление инициируемой блоком цифрового адаптера (процессором) или ПУ передачей данных между ОЗУ и ПУ;

– задание размера блока данных, который подлежит передаче, и области памяти, используемой при передаче;

– формирование адресов ячеек ОЗУ, участвующих в передаче;

– подсчет числа байт, передаваемых через интерфейс МПИ, и определение момента завершения заданной операции ввода-вывода.

Несомненно, главное место в этой структуре занимает цифровой адаптер МПИ (он же является процессором системы), который выполняет арифметические и логические операции над данными, осуществляет программное управление процессом обработки информации, организует взаимодействие всех устройств, входящих в систему. Работа адаптера происходит под воздействием сигналов синхронизации и начальной установки, поступающих по шине PCI.

Представленная структура отражает магистрально-модульный принцип организации микропроцессорных устройств и систем. Отдельные блоки являются функционально законченными модулями со своими встроенными схемами управления, выполненными в виде одного или нескольких кристаллов БИС или СБИС. Межмодульные связи и обмен информацией между модулями осуществляются посредством коллективных шин (магистралей), к которым имеют доступ все основные модули системы. В каждый момент времени возможен обмен информацией только между двумя модулями системы.

Интерфейс ЭВМ предполагает наличие информационно-логической совместимости модулей, которая реализуется путем использования единых способов представления информации, алгоритма управления обменом, форматов команд и способа синхронизации.

Все описываемые в статье блоки показаны на схеме (рисунок) в общем виде.

В работе рассмотрена структурная схема цифрового адаптера МПИ. Выделены основные блоки и узлы. Описано соединение составных частей устройства.

Описанное устройство позволяет выполнять функции ведущего устройства (процессора) в соответствии с ГОСТ 26765. 51–86.

Областью применения разработанного устройства являются специализированные системы для нужд армии и флота нашей страны, либо других стран.