В настоящее время для реализации устройств цифровой обработки сигналов (ЦОС) и в частности КИХ-фильтров наиболее востребованы такие виды устройств, как: 1) цифровые сигнальные процессоры; 2) цифровые сигнальные контроллеры; 3) ПЛИС архитектуры FPGA; 4) специализированные микросхемы. Сравним далее возможности устройств первых трёх категорий.

Цифровые сигнальные процессоры (ЦСП). ЦСП – это микропроцессорные системы, оптимизированные для выполнения операций ЦОС с максимальной производительностью. ЦСП отличаются от микропроцессоров и микроконтроллеров общего назначения дополнительными аппаратными блоками, а также модификациями базовой гарвардской архитектуры, направленными на ускорение выполнения математических операций. ЦСП обычно имеют фиксированную разрядность и формат представления чисел [1].

Для реализации алгоритма фильтрации на ЦСП должна быть составлена программа, команды которой будут выполняться последовательно одними и теми же аппаратными ресурсами. Последнее обстоятельство ограничивает производительность ЦСП и выбор архитектуры фильтра для реализации.

Наибольшую производительность среди ЦСП имеют 8–ядерные процессоры 66AKxx от Texas Instruments: 307,2 GMAC/s при максимальной тактовой частоте 1,2 ГГц [2]. Более характерны для ЦСП показатели производительности процессоров TigerSHARC от Analog Devices (тактовая частота 300 МГц, производительность 2400 MMAC/s [3]) или TMS320 от Texas Instruments (тактовая частота до 150 МГц, производительность 150 MIPS [4]).

Цифровые сигнальные контроллеры (ЦСК). ЦСК – это гибрид микроконтроллера и ЦСП. Его процессорное ядро содержит аппаратный умножитель, а среди периферийных устройств присутствуют, как правило, АЦП и ЦАП. Это позволяет реализовывать дискретные системы на одном кристалле ЦСК. С другой стороны, чаще всего разрядность АЦП и ЦАП у ЦСК не превышает 12 бит, а производительность процессорного ядра ниже, чем у ЦСП [5]. Так, например, семейство ЦСК Kinetis от NXP характеризуется максимальной тактовой частотой 100 МГц и производительностью 125 MIPS [6].

ПЛИС архитектуры FPGA. Главное преимущество ПЛИС перед ЦСП – возможность параллельного выполнения сотен и тысяч вычислительных операций. Основными ресурсами ПЛИС архитектуры FPGA (Field-Programmable Gate Array) являются массив конфигурируемых логических блоков (КЛБ), блоки ввода-вывода (БВВ) и программируемые межсоединения. Программирование ПЛИС заключается в формировании нужных соединений как внутри отдельных КЛБ и БВВ, так и между этими ресурсами.

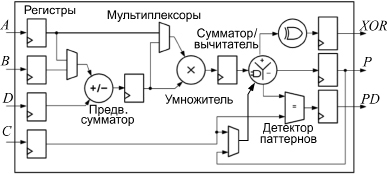

В большинстве современных FPGA присутствуют аппаратные блоки цифровой обработки сигналов (ЦОС-ячейки), количество которых может достигать нескольких тысяч. Обязательными элементами ЦОС-ячеек являются умножитель и сумматор; последний можно сконфигурировать на работу в режиме аккумулятора и реализовать тем самым на ЦОС-ячейке устройство умножения с накоплением. Вспомогательными элементами ЦОС-ячеек являются регистры и мультиплексоры (рисунок 1). Регистры используются для конвейеризации операндов; мультиплексоры – для управления выбором входных сигналов устройств ЦОС-ячейки. ЦОС-ячейки FPGA позволяют работать с операндами, представленными в форматах как с фиксированной, так и с плавающей запятой. Разрядность операндов может программироваться. ЦОС-ячейки могут объединяться в цепочки без потери производительности [1].

Структура ЦОС-ячейки FPGA

Ведущими производителями FPGA являются фирмы Xilinx (семейства Virtex, Artix, Kintex, Spartan), Intel (семейства Stratix, Arria, Cyclone), и др. Производительность устройств FPGA компании Xilinx семейства Virtex-7 с тактовой частотой 650 МГц может достигать 5053 GMAC/s [7]. А производительность последнего семейства FPGA Stratix 10 фирмы с тактовой частотой 1,5 ГГц достигает 23 TMAC/s [8].

За счёт большого количества ресурсов с программируемыми связями FPGA предоставляют свободу выбора архитектуры и параметров проектируемых фильтров. Это позволяет подбирать порядок фильтра, его разрядность и формат представления чисел таким образом, чтобы обеспечить требуемые характеристики фильтра и при этом минимизировать объём использованных ресурсов. Подобные работы могут требовать большого количества времени, однако при их выполнении можно привлекать среды математических расчётов и моделирования, например, MATLAB [9, 10].

Перечислим основные возможности реализации КИХ-фильтров на ПЛИС FPGA.

Использование программируемых ресурсов общего назначения для реализации фильтров последовательной или параллельной структур с произвольной разрядностью и порядком. В настоящее время такой вариант неактуален, поскольку даже FPGA нижнего ценового диапазона оснащены ЦОС-ячейками.

Использование программируемых ресурсов общего назначения и блочного ОЗУ для реализации фильтров с распределённой структурой, с произвольной разрядностью и порядком. Достоинствами фильтров такого типа является малая латентность вычислений, а также отсутствие потребности в умножителях. Недостатком распределённых фильтров является резкое возрастание требуемого объёма памяти с повышением порядка фильтра.

Использование встроенных ЦОС-ячеек для реализации фильтров последовательной или параллельной структур. Ячейки ЦОС позволяют сконфигурировать находящиеся там ресурсы различными способами. Такую возможность предоставляет набор мультиплексоров ячейки (рисунок). Если выбрана последовательная структура фильтра, на ЦОС-ячейке организуется аккумулятор, для чего выход P ячейки соединяется с одним из входов её сумматора. На второй вход сумматора поступает произведение очередного отсчёта фильтра на соответствующий ему коэффициент.

При реализации фильтра параллельной структуры нужное количество ячеек ЦОС объединяется в цепочку. Конкретная схема включения в цепочку каждой из ячеек определяется архитектурой фильтра (систолическая, транспонированная и др.) [12]. Например, для получения КИХ-фильтра с транспонированной структурой необходимо, чтобы в каждой из ячеек цепочки на один из входов умножителя поступал один и тот же отсчёт входного сигнала, а на другой вход подавался один из коэффициентов фильтра. На один из входов каждого из сумматоров в ячейках цепочки должно поступать полученное от умножителя произведение, а на другой – выходной сигнал P сумматора от предыдущего ЦОС-блока цепочки. Недостаток такого подхода – большой расход ячеек ЦОС при реализации фильтров высоких порядков.

В заключение сформулируем некоторые критерии выбора аппаратной платформы для реализации КИХ-фильтра. Цифровые сигнальные процессоры являются надёжным, хорошо отработанным средством для реализации КИХ-фильтров. Препятствием для применения ЦСП может стать их недостаточно высокая производительность.

Если высокая точность результатов не требуется, но важно минимизировать затраты на реализацию КИХ-фильтра, целесообразно выбирать цифровой сигнальный контроллер, который позволяет реализовать не только КИХ-фильтр, но и сопутствующие ему устройства – АЦП, ЦАП, и др.

ПЛИС FPGA позволяют получить потенциально наибольшую производительность среди рассмотренных категорий устройств, и при этом обеспечивают наибольшую свободу при выборе архитектуры фильтра и его характеристик. С другой стороны, разработка фильтра на ПЛИС может занимать много времени и требует высокой квалификации разработчика.

Библиографическая ссылка

Ведюшкина А.Е. ВОЗМОЖНЫЕ ВАРИАНТЫ АППАРАТНОЙ РЕАЛИЗАЦИИ КИХ-ФИЛЬТРОВ // Международный студенческий научный вестник. – 2018. – № 3-2. ;URL: https://eduherald.ru/ru/article/view?id=18255 (дата обращения: 20.04.2024).