В последнее время благодаря развитию программируемых логических интегральных схем (ПЛИС) появилась возможность перехода от программной к аппаратной реализации алгоритмов операционных систем (ОС), способствующая уменьшению времени выполнения алгоритма, тем самым повышая производительность вычислительной системы (ВС) в целом. Стоимость такой реализации так же значительно снижается благодаря развитию уровня элементной базы.

При проектировании МПС возникает ситуация уменьшения временных потерь, проявляющихся, при планировании процессов [1]. Частью планировщика является функция диспетчеризации задач (ДЗ) при их назначении по ЦП. В настоящей статье ДЗ реализован аппаратно, что определенно снимает проблему временных потерь [1, 2].

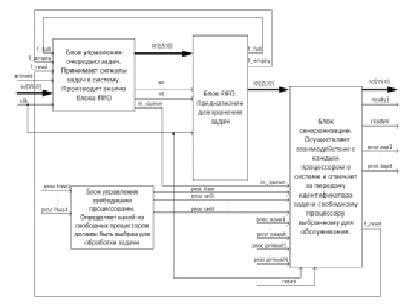

Рис. 1. Схема диспетчера задач

На рис. 1 представлены блоки:

Блок управления очередью задач, который предназначен для приема указателей (идентификаторов) задач в систему. Этот блок анализирует есть ли свободное место в очереди, и если место есть, помещает указатель новой задачи в FIFO. Также осуществляет выборку указателя задачи из очереди для обслуживания в свободном ЦП.

Блок FIFO, который предназначен для хранения указателей задач. По запросу от блока управления очередью он помещает указатель новой задачи в хвост списка или извлекает указатель задачи из головы списка для передачи его в ЦП.

Блок управления свободными ЦП – каждый ЦП, оказываясь свободным, формирует на соответствующем вывод сигнал «Свободен». Данный блок принимает подобные сигналы от всех ЦП в системе, анализирует количество свободных ЦП, и определяет по схеме приоритетов какой из свободных ЦП должен быть выбран для обработки задачи.

Блок синхронизации, в функции которого входит анализ информации о том: есть ли ожидающие задачи в системе и есть ли свободные ЦП, которые можно назначить для обработки этих задач. Данный блок осуществляет взаимодействие с каждым ЦП в системе и отвечает за передачу указателя задачи свободному ЦП, выбранному для обслуживания в соответствии с определенной схемой приоритетов.

Алгоритм разделения загрузки представляет наиболее простой и эффективный способ планирования, т.к. обладает рядом достоинств: загрузка распределяется равномерно между ЦП, обеспечивая отсутствие простоев ЦП при наличии готовых к выполнению задач; простота представления и высокая степень понятности алгоритма функционирования планировщика, заключающаяся в том, что когда ЦП освобождается, он вызывает функцию назначения задач из ОС.

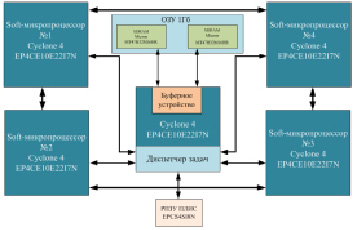

Аппаратный ДЗ реализован на языке VHDL и входит в состав РВС, базирующийся на ПЛИС Cyclone 4 фирмы Altera, на данных интегральных схемах конфигурируются софт-микропроцессорные ядра NIOS II, одна из ПЛИС используется для реализации ДЗ, ОЗУ 1 Гб состоит из двух банков памяти по 512 Мб. РВС – ВС, элементная база, которой состоит из множества соединенных между собой ПЛИС большой интеграции, образующих единое вычислительное поле. РВС благодаря гибкой архитектуре системы обеспечивает реальную производительность при решении вычислительно трудоемких задач, к которым относятся задачи цифровой обработки сигнала. РВС предназначена для конфигурирования архитектуры под различные классы задач цифровой обработки сигнала. Данные задачи находят применение в следующих отраслях: образование – обучение и исследование высокопроизводительных вычислительных систем, цифровая обработка сигнала; медицина – обработка графической информации и обработка базы данных больниц; геоинформационные системы – оцифровка карт, обработка картографических данных и т.д.; охранные системы – интеллектуальные охранные системы; военные структуры – шифраторы каналов передачи информации, автоматические системы наведения и т.д.

Рис. 2. Схема РВС

Введение в РВС аппаратной реализации ДЗ позволит повысить производительность и значительно снять проблему временных потер при планировании процессов и задач, что положительно повлияет на производительность системы в целом.

Библиографическая ссылка

Мартенс-Атюшев Д.С., Мартышкин А.И. РАЗРАБОТКА И ИССЛЕДОВАНИЕ РЕКОНФИГУРИРУЕМОЙ СИСТЕМЫ ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛА // Международный студенческий научный вестник. – 2016. – № 3-1. ;URL: https://eduherald.ru/ru/article/view?id=14733 (дата обращения: 27.04.2024).